DDR的一些分享

DDR简述

什么是DDR

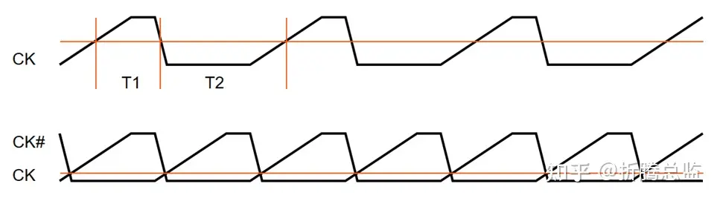

- DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,双数据率同步动态随机存储器)通常被我们称为DDR,其中的“同步”是指内存工作需要同步时钟,内部命令的发送与数据传输都以它为基准。DDR是一种掉电就丢失数据的存储器件,并且需要定时的刷新来保持数据的完整性。

- DDR:双倍频采样

- S:数据时钟与命令时钟同步

- D:需要刷新

- R:地址可以随机

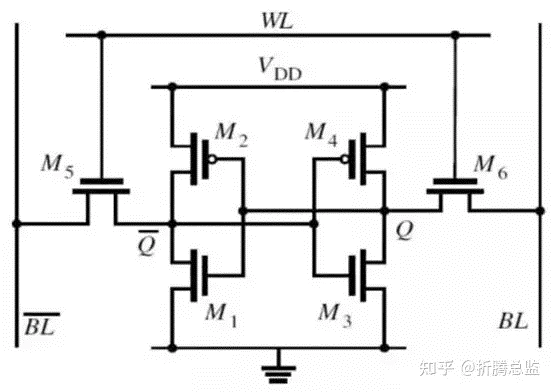

SRAM

1963年,仙童半导体公司的罗伯特·诺曼(Robert Norman)设计了双极型晶体管静态随机访问存储器(BJT SRAM),每一位均需要6个三极管组成。一年后,飞兆半导体推出了 MOS 型 SRAM。SRAM 存储数据后,只要不断电,数据就能一直保持

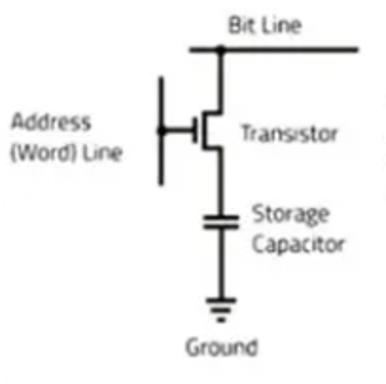

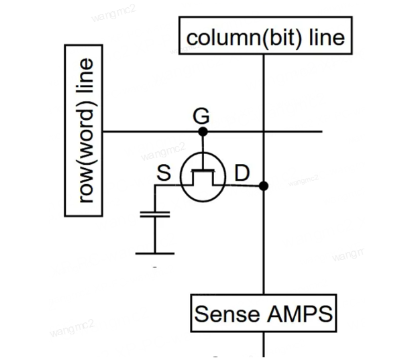

DRAM

DRAM主要通过一个电容和一个三极管组成,可以选择打开指定某条 Wordline 上的所有 MOS 管,让对应的电容器的电荷流入各自的 Bitline 线上,检测 Bitline 电平状态即可知道存储的信息。写入也类似,打开 MOS 管后,把要写入的电平加持到 Bitline,即可对存储电容充以给定的电平。但是,电容会缓慢漏电,我们必须想办法,定期给电容刷新电量,写入原来的电平。

区别

SDRAM

- SDRAM相对于DRAM,多了一个同步的概念,指DDR的数据时钟于CPU的时钟是同步的,当前此概念已落后,目前指的是CA时钟于数据时钟是同步的,于LPDDR5而言,即CK与WCK同源,这样做的好处会在后续DDR读写操作中体现。

当前DDR均是只SDRAM

为什么是双边沿

DDR的演进

| 标准 | 传输速率 | 核心频率 | Prefetch | 总线频率 | 最大位宽 | 电压 (V) |

|---|---|---|---|---|---|---|

| SDR | 100–166 | 100–166 | 1n | 100–166 | 16/16 | 3.3 |

| DDR | 200–400 | 100–200 | 2n | 100–200 | 16/32 | 2.5, 2.6 |

| DDR2 | 400–1066 | 100–266 | 4n | 200–533 | 16/64 | 1.8, 1.55 |

| DDR3 | 800–2133 | 100–266 | 8n | 400–1066 | 16/128 | 1.5, 1.35 |

| DDR4 | 1600–3200 | 200–400 | 8n | 800–1600 | 16/128 | 1.2 |

| DDR5 | 4800-8400 | 300-525 | 16n | 2400–4200 | 16/256 | 1.1 |

关键概念

关键字

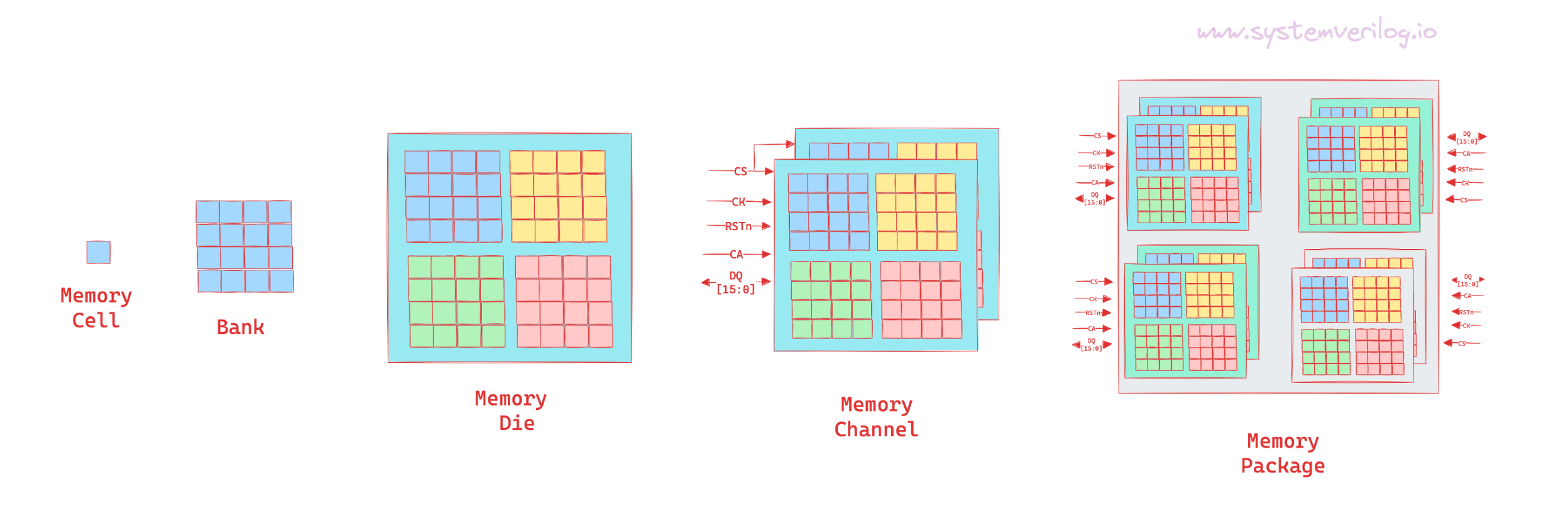

- Cell

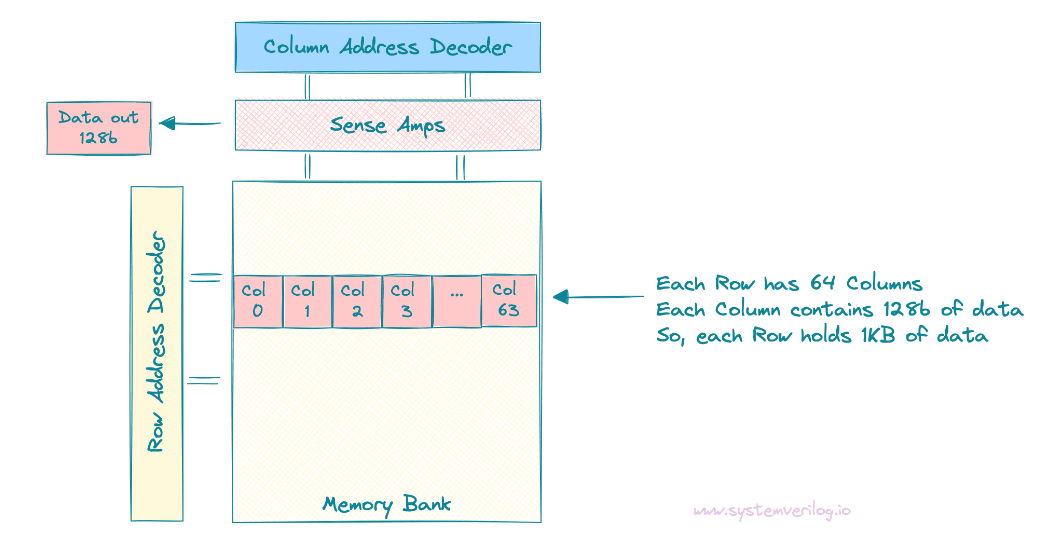

- Row

- Column

- Array

- Bank

- Bank Group

- Die

- Chip

Channel

cell

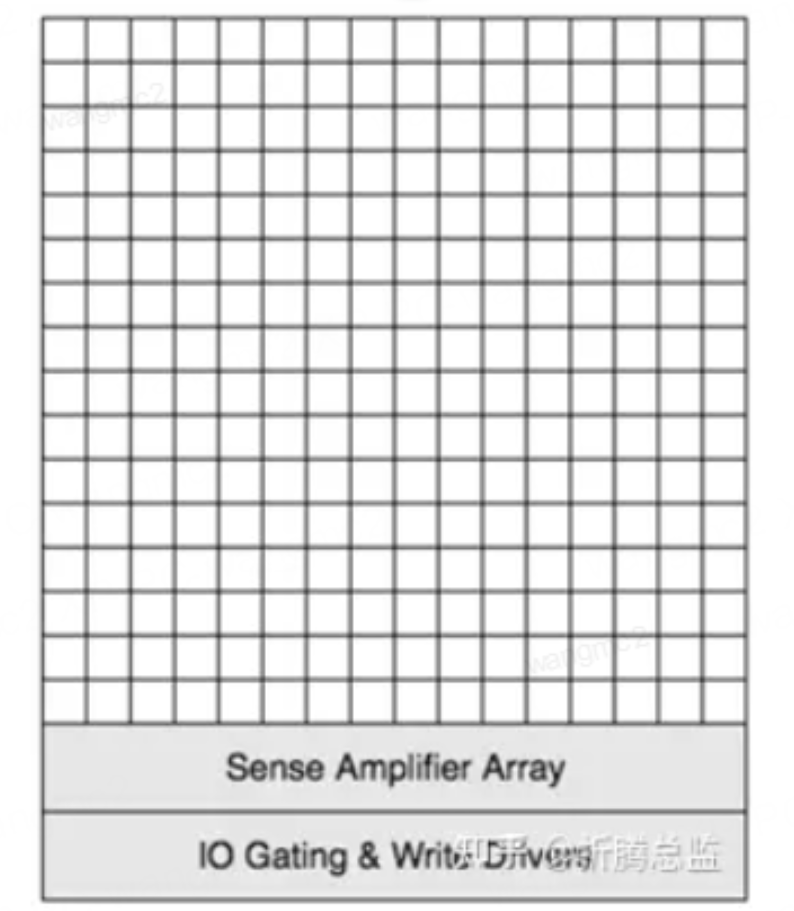

ARCH

Array

Bank

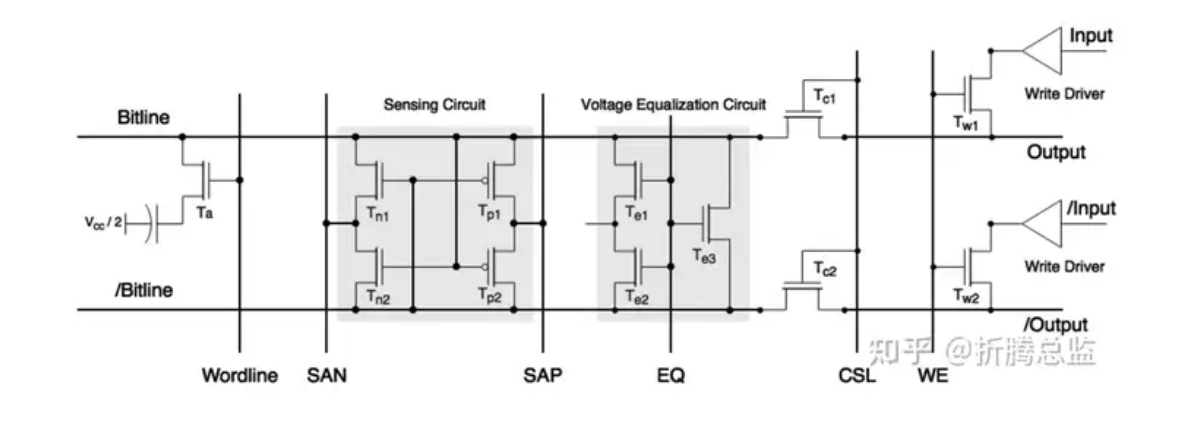

cell 细节

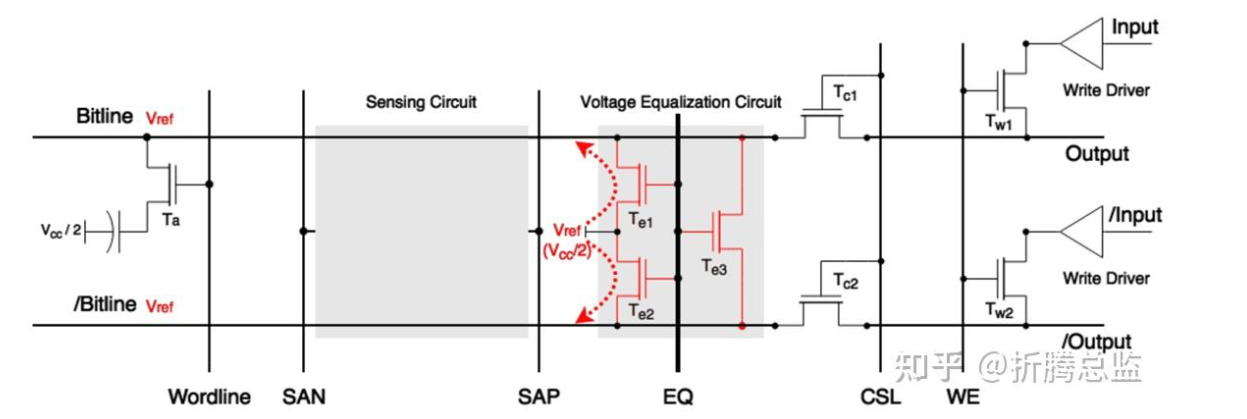

上图中,各信号线作用如下:

- SAN:感知放大负极,连接 GND,与 SAP 构成差分共同作用

- SAP:感知放大正极,连接 Vcc,与 SAN 构成差分共同作用

- EQ: 均衡控制信号线,在预充电阶段把 Bitline 线对拉到参考电平

- CSL:列选信号,在读写操作前、选中某一行后,通过 CSL 选中具体的列(打开 Bitline)

- WE:写使能信号,在写操作时,使能该信号,可以把要写入的数据电平加持到 Bitline 线对上,完成对指定 Cell 电容器充电

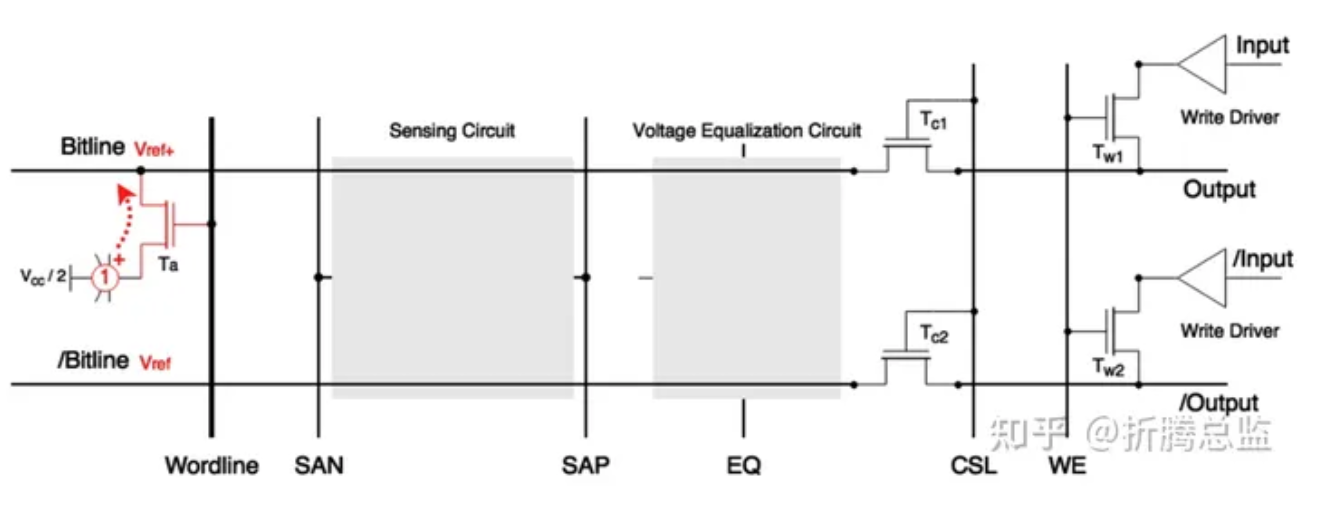

Precharge

Precharge作用:

确保bitline为参考电压,防止之前的操作,残留电荷,影响数据读写;

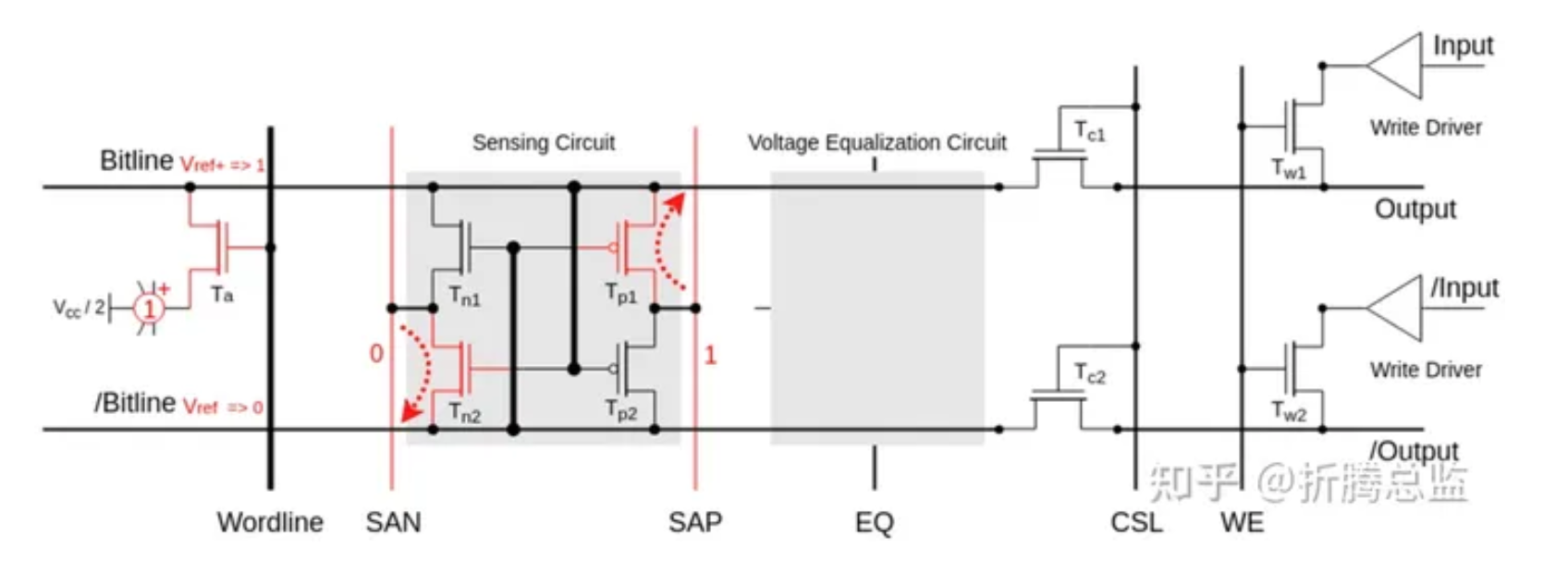

访问阶段

wordline拉起,cell中的电压传递到bitline

感知阶段

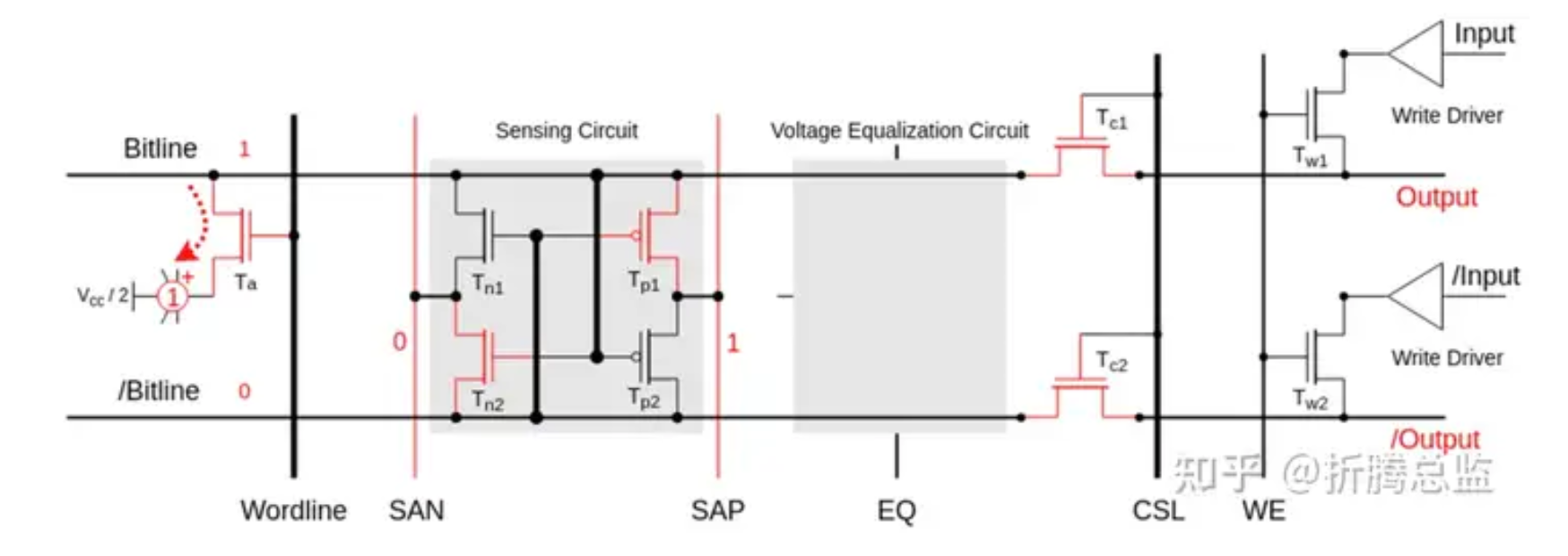

恢复阶段

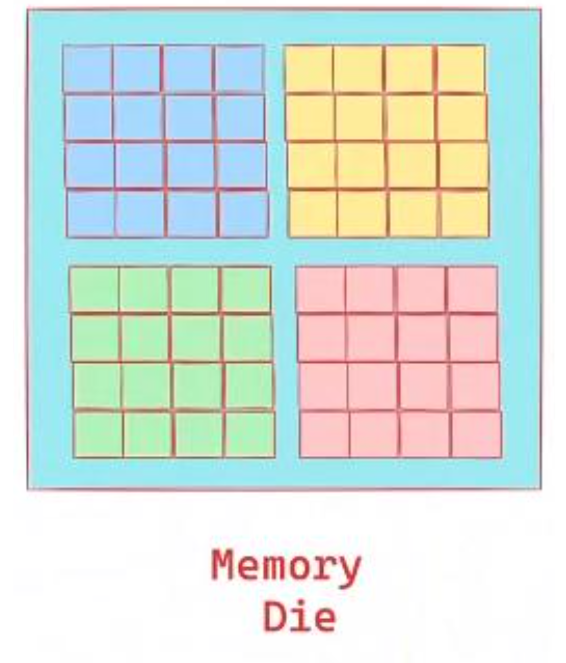

Die

Die主要由多个Bank或过个Bank Group组成

Chip

CHIP一般由多个Die组成

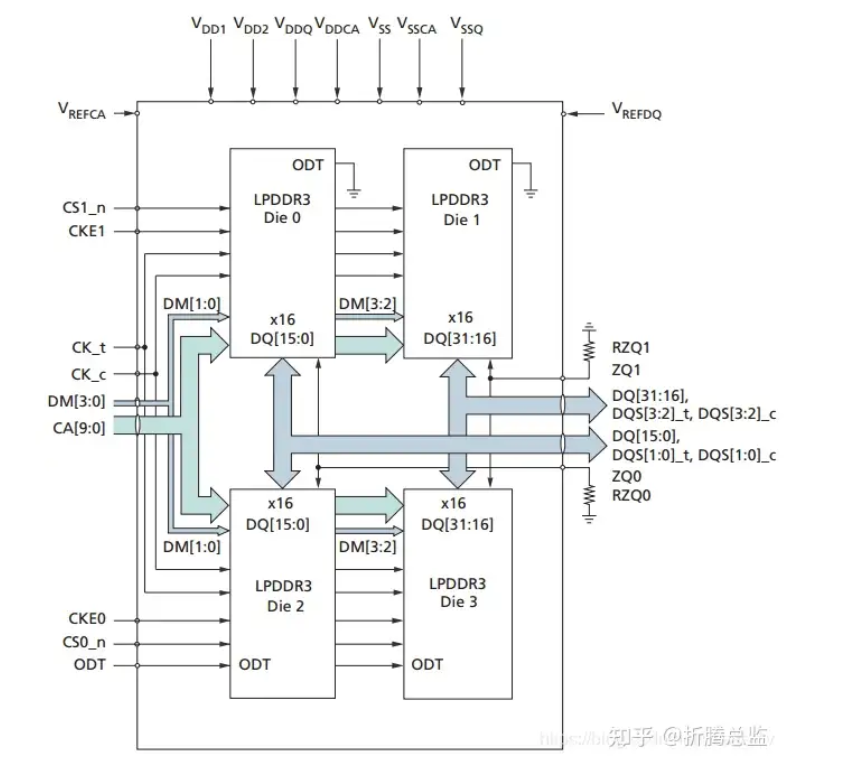

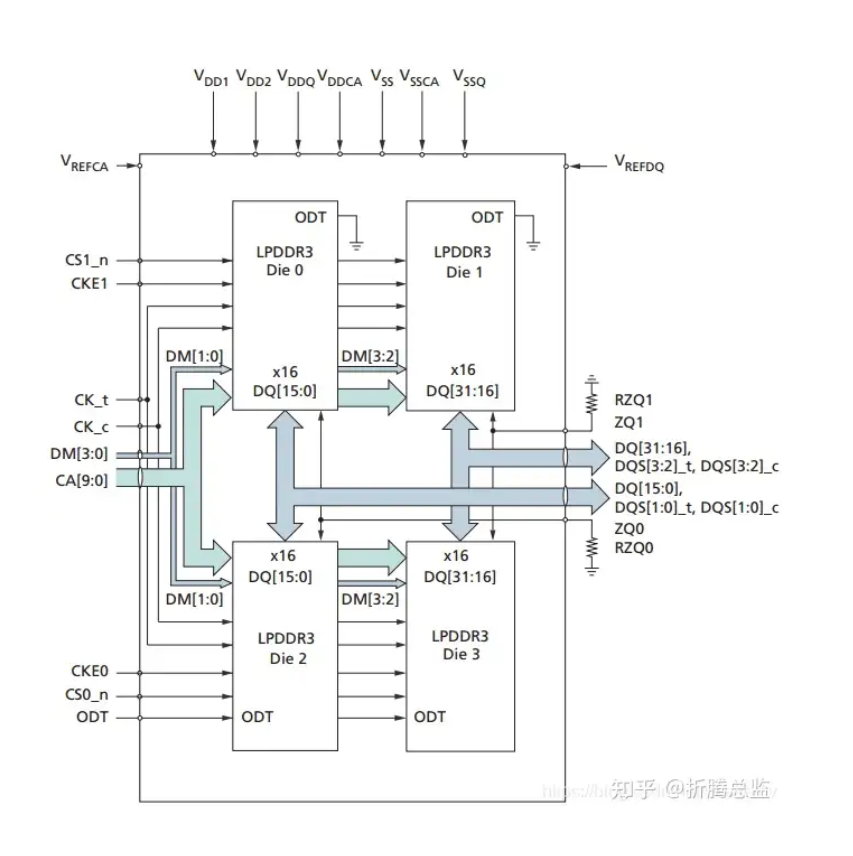

Rank与Channel

双RANK 单channel 位宽32bit

双rank 双channel 位宽16 bit

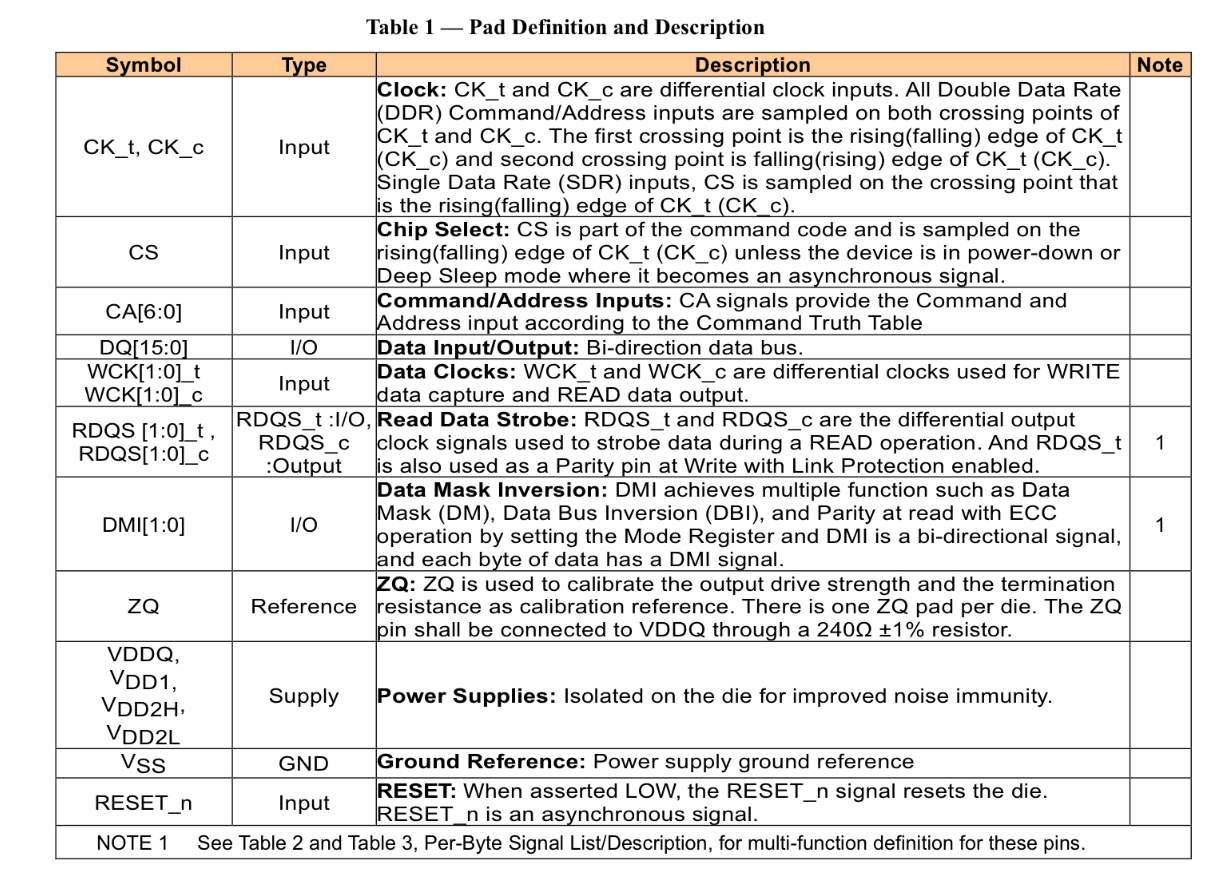

关键接口信号-以LPDDR5举例

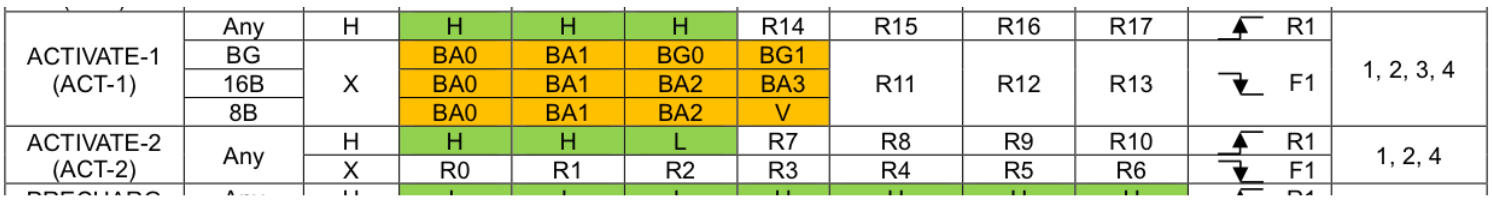

常用操作

- Row Active

- Column Read

- Column Write

- Precharge

- Row Refresh

- ZQ Calibration

- Verf DQ Calibraton

- Write Leveling

- CA training

- Read Training

Write Training

Row Active

Row Active主要用于激活相关Bank,Bank Group,使能相关word line,使电容数据传递至放大器,为读写操作做准备。

Read

RL Read Latency 表示在发出读取的命令之后需要多久在DQ上正确的获取到数据;

关键步骤

- Precharge

- ACT 选中相关的行

- 感知

- 选中相关列,读取

- 写回

Write

WL Write Latency 表示在发出写入的命令之后需要多久在DQ上正确的获取到数据;

关键步骤

- Precharge

- ACT 选中相关的行

- 感知

- 选中相关列,读取

- 合并写入的数据

写回

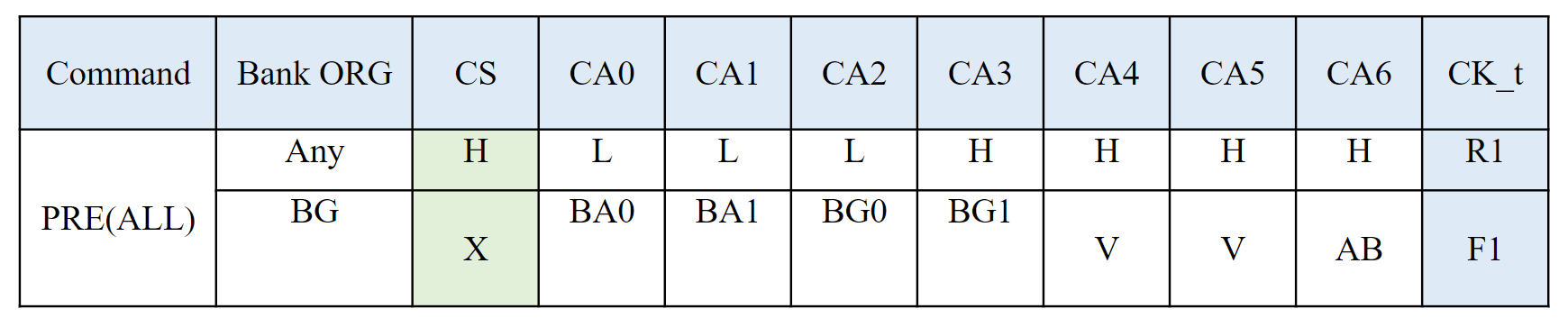

Precharge

用于关闭一个被打开的bank,切换row访问数据时需要做Precharge操作,可以关闭单个或者所有bank

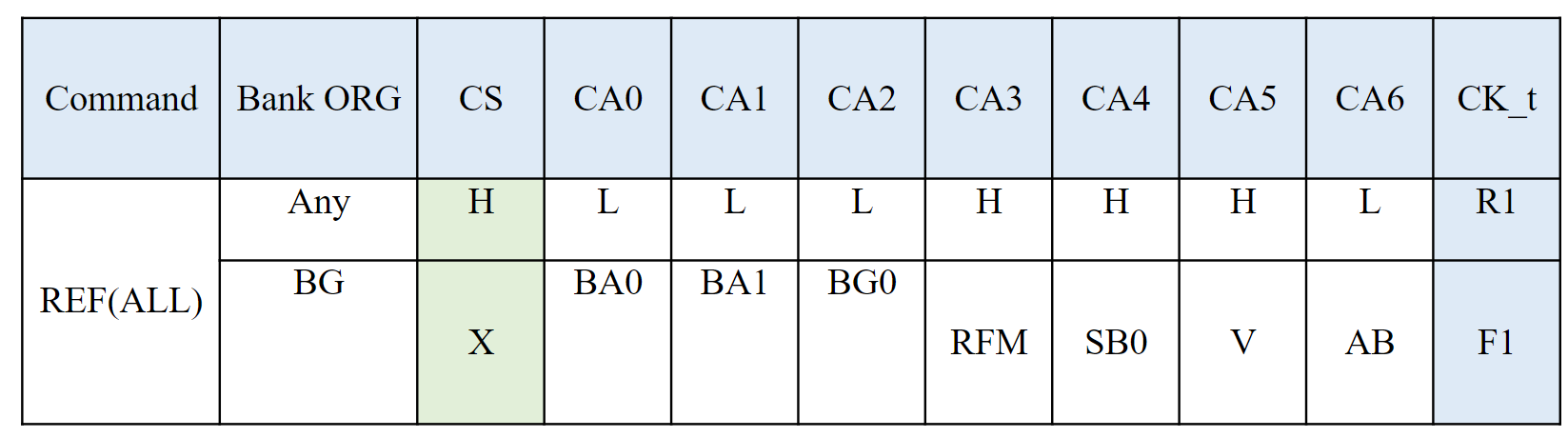

Refresh

防止电容上面存放的数据掉电丢失信息,需要对memory里面的数据进行周期性刷新

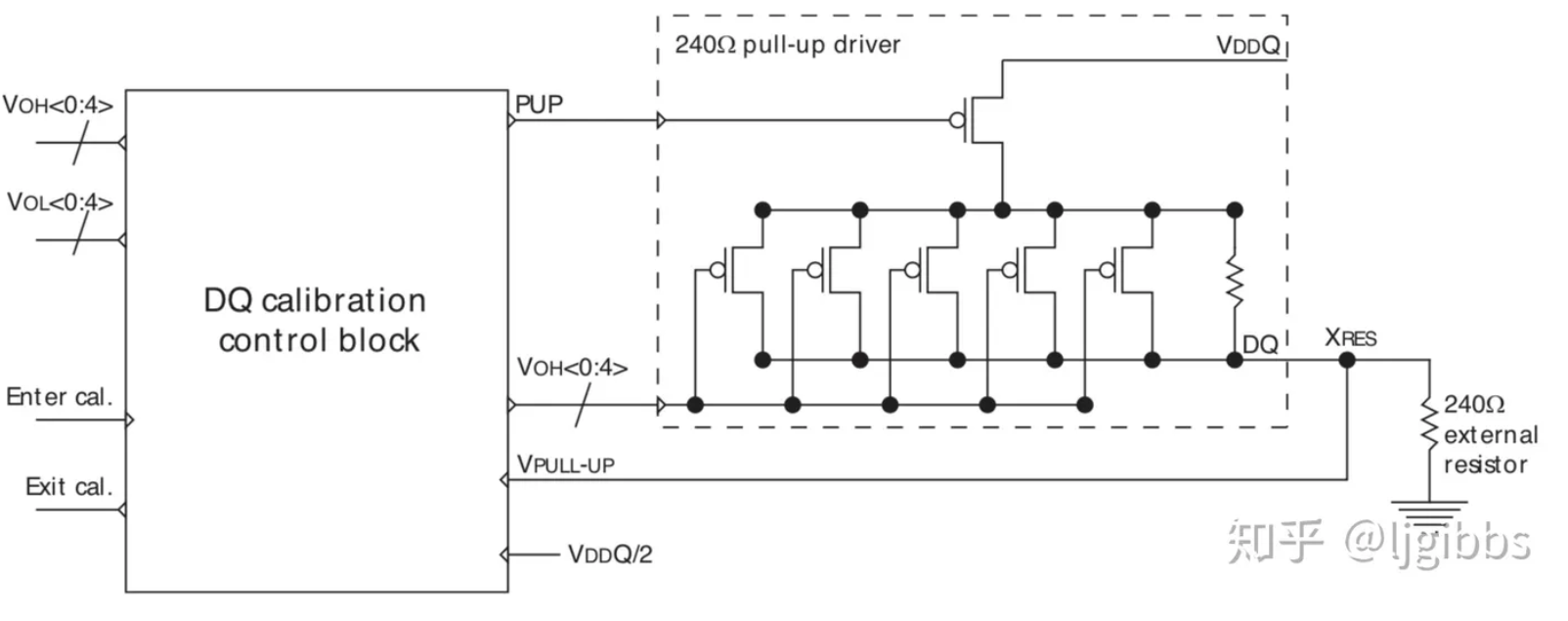

ZQ Calibration

为什么需要做ZQ校准

- DRAM颗粒需要这些240欧姆的电阻提高信号完整性,考虑阻抗匹配;

- 由于CMOS工艺限制无法时精准的240欧姆;

受温度,PCB走线等影响,也会影响到阻值的变化;

ZQ校准流程

- 发送ZQ校准命令;

- ZQ校准模块调整VOH使得;

- ZQ校准模块检测DQ电压,直到DQ电压为Vddq/2;

- ZQ校准结束;

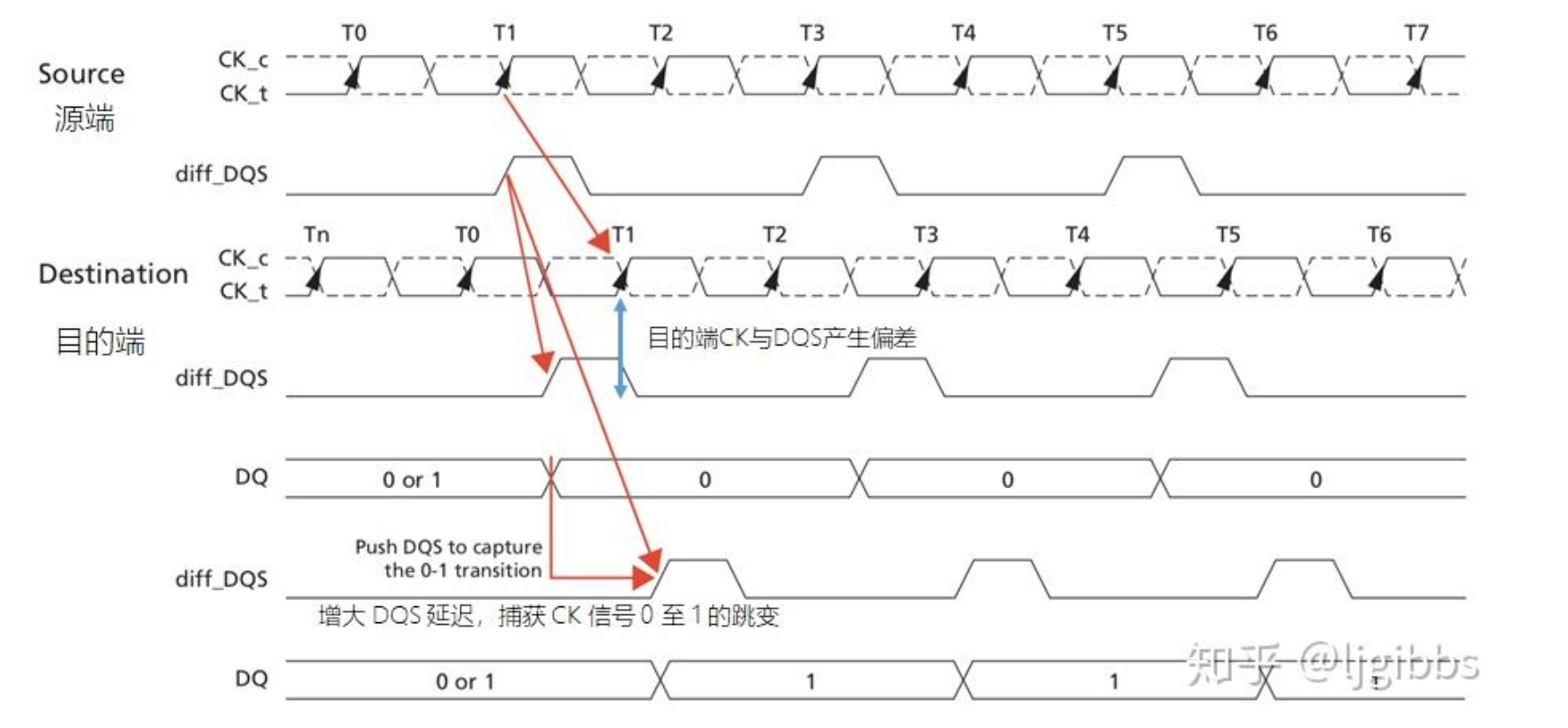

Write Leveling

主要作用

在进行数据读写时,存在tWL,即固定CK拍数去写入DQ数据,但是由于PCB走线的原因,导致CK与WCK产生相位差,这里采用Write Leveling重新对齐CK与WCK;

实现过程

- 设置mode register进入Write Leveling 模式;

- 控制器发送WCK(or DQS)信号,WCK(DQS)采样CK;

- 控制器调节WCK(DQS)延时,并读取DQS采样到的CK值;

- 不断重复2,3,直到读取的CK值,从0变化到1,说明WCK(DQS)与CK上升沿对齐;

- Write Leveling 完成;

CS&CA training

CA Training目的

- PCB走线可能会导致导致CK与CS,CS与CA之间存在延时差异,通过CA与CS training消除这种差异;

- CS信号需要确保CK采到的是其中间位置;

CA信号,应通过VERF训练,且CA信号需要确保CK信号采到的是其中间位置;

Training过程

- 写入颗粒MR,配置为一个未使用的频率;

- 进入training mode(写MR)

(通过CS与CA发送数据 – mode1&mode2)(使能DMI[low]配置DQ为VERF的值 – mode2); - DQ静态输出CA与CS传输的数据;

- HOST不断修改Delay与VERF(mode2),并分析,得到最佳值;

Training结束;

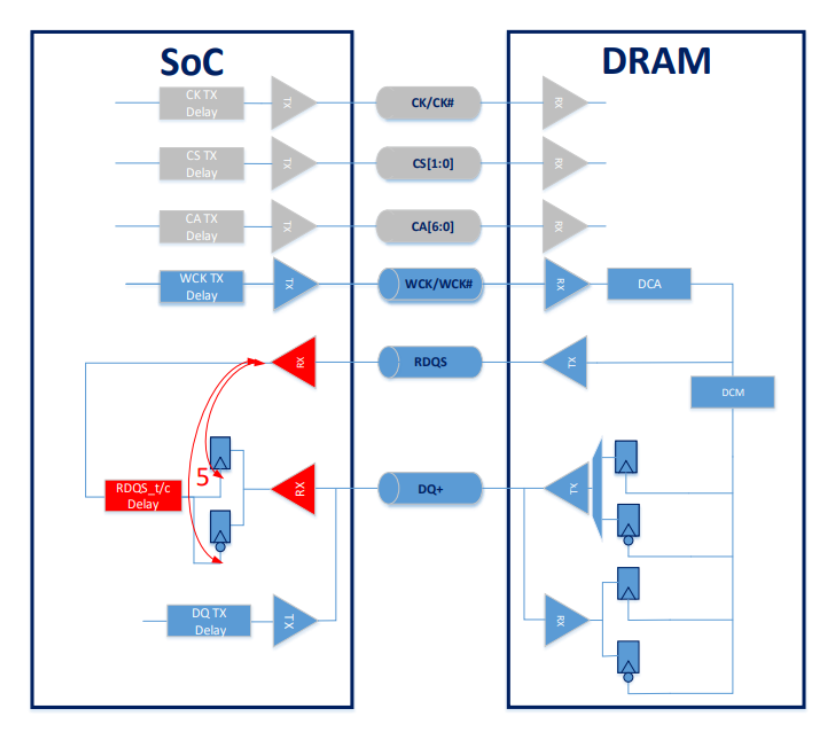

Read Training

Training目的

- 训练控制器的读采样电路,在读数据眼图的中央进行采样,以获得最稳定的采样结果;

训练过程

- 写入相关MR写入相关patterns;

- 通过DQ读取相关patterns;

- 不断更改RDQS相关的Delay以及Verf;

- 记录相关Delay值及Verf值,以得到最佳值;

- Training结束;

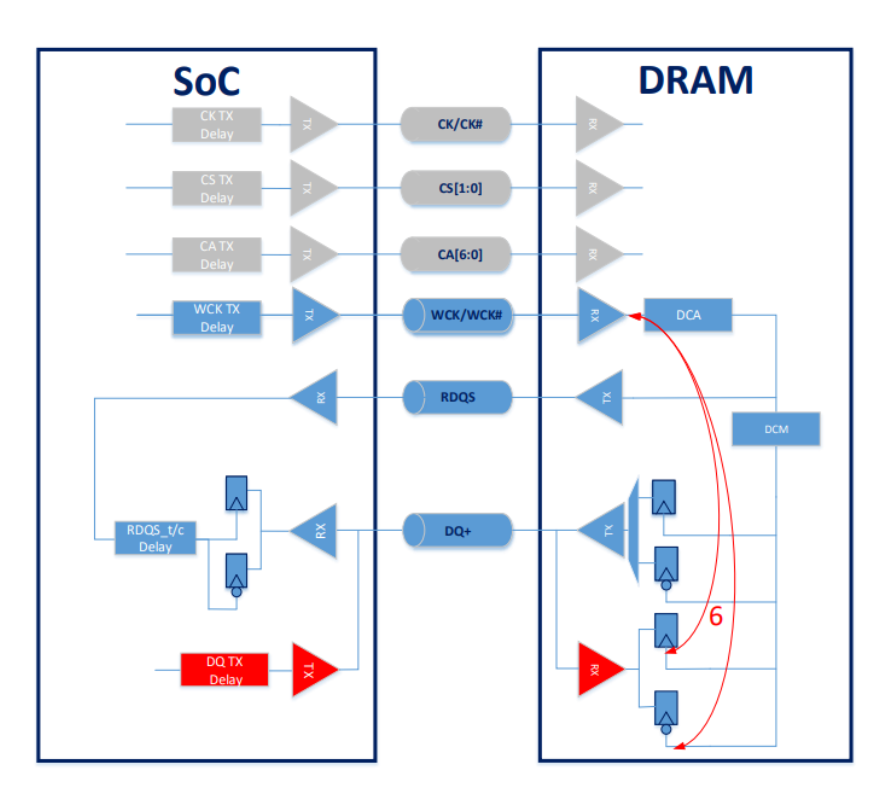

Write Training

Training目的

通过调整DQ的延时,以及Verf,使得采样达到一个最佳的状态;

Training过程

- 在已经进行Read Training的前提下;

- 通过对DRAM中的FIFO进行发送读写pattern;

- 不断调整DQ的delay及Verf;

- 记录不同Delay及Verf,得到最佳的配置值;

- Training结束;

新车首发,新的一年,只带想赚米的人coinsrore.com

新车首发,新的一年,只带想赚米的人coinsrore.com

2025年10月新盘 做第一批吃螃蟹的人coinsrore.com

新车新盘 嘎嘎稳 嘎嘎靠谱coinsrore.com

新车首发,新的一年,只带想赚米的人coinsrore.com

新盘 上车集合 留下 我要发发 立马进裙coinsrore.com

做了几十年的项目 我总结了最好的一个盘(纯干货)coinsrore.com

新车上路,只带前10个人coinsrore.com

新盘首开 新盘首开 征召客户!!!coinsrore.com

新项目准备上线,寻找志同道合的合作伙伴coinsrore.com

新车即将上线 真正的项目,期待你的参与coinsrore.com

新盘新项目,不再等待,现在就是最佳上车机会!coinsrore.com

新盘新盘 这个月刚上新盘 新车第一个吃螃蟹!coinsrore.com

2025年10月新盘 做第一批吃螃蟹的人coinsrore.com

新车新盘 嘎嘎稳 嘎嘎靠谱coinsrore.com

新车首发,新的一年,只带想赚米的人coinsrore.com

新盘 上车集合 留下 我要发发 立马进裙coinsrore.com

做了几十年的项目 我总结了最好的一个盘(纯干货)coinsrore.com

新车上路,只带前10个人coinsrore.com

新盘首开 新盘首开 征召客户!!!coinsrore.com

新项目准备上线,寻找志同道合 的合作伙伴coinsrore.com

新车即将上线 真正的项目,期待你的参与coinsrore.com

新盘新项目,不再等待,现在就是最佳上车机会!coinsrore.com

新盘新盘 这个月刚上新盘 新车第一个吃螃蟹!coinsrore.com

2025年10月新盘 做第一批吃螃蟹的人coinsrore.com

新车新盘 嘎嘎稳 嘎嘎靠谱coinsrore.com

新车首发,新的一年,只带想赚米的人coinsrore.com

新盘 上车集合 留下 我要发发 立马进裙coinsrore.com

做了几十年的项目 我总结了最好的一个盘(纯干货)coinsrore.com

新车上路,只带前10个人coinsrore.com

新盘首开 新盘首开 征召客户!!!coinsrore.com

新项目准备上线,寻找志同道合 的合作伙伴coinsrore.com

新车即将上线 真正的项目,期待你的参与coinsrore.com

新盘新项目,不再等待,现在就是最佳上车机会!coinsrore.com

新盘新盘 这个月刚上新盘 新车第一个吃螃蟹!coinsrore.com

华纳公司合作开户所需材料?电话号码15587291507 微信STS5099

华纳公司合作开户所需材料?电话号码15587291507 微信STS5099

华纳公司合作开户所需材料?电话号码15587291507 微信STS5099

华纳公司合作开户所需材料?电话号码15587291507 微信STS5099

华纳公司合作开户所需材料?电话号码15587291507 微信STS5099

华纳公司合作开户所需材料?电话号码15587291507 微信STS5099

华纳公司合作开户所需材料?电话号码15587291507 微信STS5099

华纳公司合作开户所需材料?电话号码15587291507 微信STS5099

华纳东方明珠客服电话是多少?(▲18288362750?《?微信STS5099? 】

如何联系华纳东方明珠客服?(▲18288362750?《?微信STS5099? 】

华纳东方明珠官方客服联系方式?(▲18288362750?《?微信STS5099?

华纳东方明珠客服热线?(▲18288362750?《?微信STS5099?

华纳东方明珠24小时客服电话?(▲18288362750?《?微信STS5099? 】

华纳东方明珠官方客服在线咨询?(▲18288362750?《?微信STS5099?

果博东方客服开户联系方式【182-8836-2750—】?薇- cxs20250806】

果博东方公司客服电话联系方式【182-8836-2750—】?薇- cxs20250806】

果博东方开户流程【182-8836-2750—】?薇- cxs20250806】

果博东方客服怎么联系【182-8836-2750—】?薇- cxs20250806】

果博东方客服开户联系方式【182-8836-2750—】?薇- cxs20250806】

果博东方公司客服电话联系方式【182-8836-2750—】?薇- cxs20250806】

果博东方开户流程【182-8836-2750—】?薇- cxs20250806】

果博东方客服怎么联系【182-8836-2750—】?薇- cxs20250806】